1991

1. The program given below is run on an 8085 based

microcomputer system. Determine the contents of the registers: PC, SP, B, C, H,

L after a halt instruction is executed.

Answer: PC = 3001, SP = 0FFE, B = 20H, C = 0BH, H = 2FH and L = 38H

1992

1. In an 8085 microprocessor system with memory mapped I/O,

a.

I/O devices have 16 bit

addresses

b.

I/O devices are accessed using IN

and OUT instructions

c.

There can be a maximum of 256 input

devices and 256 output devices

d.

Arithmetic and logic operations can

be directly performed with the I/O data.

Answer: A

2. The following program is run on 8085 microprocessor:

At the completion of the execution of the program, the

program counter of the 8085 contains _____________ and the stack pointer

contains _______________.

Answer: SP = 0FFC, PC = 200A

3. Figure shows the memory circuit of 8085 microprocessor.

a.

What is the total size of the memory

in the circuit?

b.

What are the beginning and ending

addresses of the memory in chip 1?

c.

What are the beginning and ending

addresses of the memory in chip 2?

d.

Are the memory chips in the circuit

ROM or RAM?

e.

How will you replace the two NAND

gates I the circuit with one 3 to 8 decoder

without changing the memory size or the memory addresses? Assume that the decoder has one active high

enable E1 and one active low enable E2.

1993

1. In a microprocessor, wait states are used to

a.

Make the processor wait during a DMA

operation

b.

Make the processor wait during an

interrupt processing

c.

Make the processor wait during a

power shutdown

d.

Interface slow

peripherals to the processor

Answer:D

2. A microprocessor has

five address lines [A4 – A0] and eight data lines [D7

– D0]. An input device A, an output device B, a ROM and a RAM are

memory mapped to the microprocessor at the addresses as shown in figure.

Devices A and B have four addressable registers each/ RAM has 8 bytes and ROM

has 16 bytes.

a.

Indicate the address lines to be

connected to each device and memory.

b.

Obtain the minimum sum of product

expression for the chip select (CS) function

of each device/memory.

1995

1. When a CPU is interrupted, it

a.

Stops executing of instructions

b.

Acknowledges interrupt and branches

of subroutine

c.

Acknowledges interrupt and continues

d.

Acknowledges interrupt and waits for

the next instruction from the interrupt device

Answer: B

2. A ‘DMA’ transfer

implies

a.

Direct transfer of data between

memory and accumulator

b.

Direct transfer of data between

memory and I/O devices without use of µP

c.

Transfer of data exclusively within µP registers

d.

A fast transfer of data between µP and I/O devices

Answer: B

Solution:

3. An ‘Assembler’ of a microprocessor is used for

a.

Assembly of processors in a

production line

b.

Creation of new program’s using

different modules

c.

Translation of a program form

assembly language to machine language

d.

Translation of a higher level

language into English text

Answer: C

4. A hypothetical CPU has a parallel address bus, a parallel

data bus, a RD and WR active LOW signals. Two ROMs of size 4K words each and

two RAMs of sizes 16K and 8K words, respectively, are to be connected to the

CPU. The memories are to be so connected that they fill the address space of

the CU as per the memory map shown in the figure. Assuming tat chip select

signals are active LOW.

a.

What is the number of lines in the

address bus of the CPU?

b.

Determine the values of address X,

Y, Z and W as decimal numbers.

c.

Using a 2 to 4 decoder and some

additional gates, draw a circuit for the decoding

logic.

1996

1. The total number of memory accesses involved (inclusive of the op-code fetch), when an

8085 processor executes the instruction LDA 2003 is

a.

1

b.

2

c.

3

d.

4

Answer: D

Solution :

2. The following sequence of instructions are executed by an

8085 microprocessor:

1000 LXI SP, 27FFH

1003 CALL 1006

1006 POP H

The contents of the stack pointer (SP) and the HL register

pair on completion of execution of these instructions are

a.

SP = 27FF, HL = 1003

b.

SP = 27FD, HL = 1003

c.

SP = 27FF, HL = 1006

d.

SP = 27FD, HL = 1006

Answer: C

Solution :

1997

1. In 8085 µP

system, the RST instruction will cause an interrupt

a.

Only if an interrupt service routine

is not being executed

b.

Only if a bit in the interrupt mask

is made 0

c.

Only if interrupts have been enabled

by an EI instruction

d.

None of the above

Answer: C

Solution :

2. The decoding circuit is shown in figure, has been used to

generated the active low chip select signal for a microprocessor peripheral

(The address lines are designated as A0 to A7 for I/O

addresses).

a.

60H – 63H

b.

A4 – A7H

c.

30 – 33H

d.

70 – 73H

3. The following instructions have been executed by an 8085 µP

For which address will the next instruction be fetched?

a.

6019

b.

6379

c.

6979

d.

None of the above

Answer: C

Solution :

4. A signed integer has been stored in a byte using the 2’s

complement format. We wish to store the same integer in a 16 bit word. We

should

Answer: C

5. Match the following, while moving data between registers of

the 8085 and the stack

Answer: 1 - c, 2 - d

Solution :

6.

An 8085 µP uses a 2 MHz crystal. Find the time taken by it to execute

the following delay subroutine, inclusive of the call instruction in the

calling program.

You are given that a CALL

instruction takes 18 cycles of the system clock, PUSH requires 12 cycles and

conditional jump takes 10 cycles if the jump is taken and 7 cycles if it is

not. All other instructions used above take (3n + 1) clock cycles, where n is

the number of accesses to the memory, inclusive of the opcode fetch.

Answer: 1.842 mSec

Solution :

1998

1. An I/O processor control the flow of information between

a.

Cache memory and I/O devices

b.

Main memory and I/O devices

c.

Two I/O devices

d.

Cache and main memory

Answer: B

2. An instruction used to set the carry flag in a computer can

be classified as

a.

Data transfer

b.

Arithmetic

c.

Logical

d.

Program control

Answer: C

3. Write a short assembly language program, without using any

arithmetic instruction, to store hexadecimal 5D in the flag register of 8085

microprocessor. Data in other registers of the processor must not alter upon

executing this program.

Answer:

PUSH H

MOV H, A

MOV L, 5DH

PUSH H

POP PSW

POP H

PUSH H

MOV H, A

MOV L, 5DH

PUSH H

POP PSW

POP H

Solution :

1999

1. If CS = A15’A14A13 is used

as the chip select logic of a 4K RAM in an 8085 system, then its memory range

will be

a.

3000 – 3FFFFH

b.

7000 – 7FFFH

c.

5000 – 5FFFH and 6000 – 6FFFH

d.

6000 – 6FFFH and 7000 – 7FFFH

Answer: D

2. An 8085 assembly language program is given below.

Answer: (a) this program will found the highest number present in the given memory location, finally that highest number will present in the accumulator.

(b) (i) A = 2B, B = 2B, C = 00, HL = 2002

(ii) CY = 1 and ZF = 1

(iii) [2000] = 18H, [2001] = 10H, [2002] = 2BH and [2100] = 2BH

(b) (i) A = 2B, B = 2B, C = 00, HL = 2002

(ii) CY = 1 and ZF = 1

(iii) [2000] = 18H, [2001] = 10H, [2002] = 2BH and [2100] = 2BH

Solution :

2000

1.

In the 8085 microprocessor, the RST

6 instruction transfers the program execution to the following location

a.

30H

b.

24H

c.

48H

d.

60H

Answer: A

2. The number of hardware interrupts (which require an external

signal to interrupt) present in an 8085 microprocessor are

a.

1

b.

4

c.

5

d.

13

Answer: C

3. The contents of register (B) and Accumulator (A) of 8085

microprocessor are 49H and 3AH respectively. The contents of A and the status

of carry flag (CY) and sign flag (S) after executing SUB B instruction are

a.

A = F1 , CY = 1 , S = 1

b.

A = 0F, CY = 1, S = 1

c.

A = F0, CY = 0, S = 0

d.

A = 1F, CY = 1, S = 1

Answer: A

4. The program and machine code for an 8085 microprocessor are

given by

The starting address of the above program is 7FFFH. What

would happen if it is executed from 8000H?

Answer: (a) if the program executes from 8000H, it will find an infinite loop with only one instruction "JMP 8000", an unconditional jump to memory location 8000.

(b) Number of machine cycles required for CALL 2000H and LDA 2000H are 5 and 4 respectively.

(c) XRA A and SUB A

(b) Number of machine cycles required for CALL 2000H and LDA 2000H are 5 and 4 respectively.

(c) XRA A and SUB A

Solution :

2001

1. An 8085 microprocessor based system uses a 4K x8 bit RAM

whose starting address is AA00H. The address of the last byte in this RAM is

a.

0FFFH

b.

1000H

c.

B9FFH

d.

BA00H

Answer: C

2. Consider the following sequence of instructions for an 8085

microprocessor based system.

a. If the program execution begins at the location FF00H, write

down the sequence of instructions

which are actually executed till a HLT instruction. Assume all Flags are initially RESET.

b. Which of the three ports (PORT1, PORT2 and PORT3) will be loaded

with data, and what is the bit

pattern of the data?

Answer: (b) port 2 with data 03H

Solution :

2002

1. Consider the following assembly language program.

MVI B, 87H

MOV A, B

START: JMP

NEXT

MVI B, 00H

XRA B

OUT PORT1

HLT

NEXT: XRA B

JP START

OUT PORT2

HLT

The execution of the above program in an 8085 microprocessor

will result in

a.

An output of 87H at PORT1

b.

An output of 87H at PORT2

c.

Infinite looping of the program

execution with accumulator data remaining at 00H

d.

Infinite looping of the program

execution with accumulator data alternating between

00H and 87H

Answer: B

2. An 8085 microprocessor operating at 5 MHz clock frequency

executes the following routine.

START: MOV A,

B

OUT 55H

DCR B

STA FFF8H

JNP START

a.

Determine the total number of

machine cycles required to execute the routine till

the JMP instruction is executed for the first time.

b.

Determine the time interval between

two consecutive (MEMW)’ signals.

c.

If the external logic controls the

READSY line so that three WAIT states are introduced

in the I/O WRITE machine cycle, determine the time interval between two consecutive (MEMW)’ signals.

Answer: (a) 21 (b) 41 (c) 44

Solution :

2003

1. In an 8085 microprocessor, the instruction CMP B has been

executed while the content of the accumulator is less than that of register B.

As a result,

a.

Carry flag will be set but Zero flag

will be reset

b.

Carry flag will be reset but Zero

flag will be set

c.

Both Carry flag and Zero flag will

be reset

d.

Both Carry flag and Zero flag will

be set

Answer: A

2004

1. The 8255 programmable peripheral interface is used as

described below.

(i)

An A/D converter is interfaced to a

microprocessor through an 8255. The conversion

is initiated by a signal from the 8255 on port C. A signal on port C. A signal on port C causes data to be

strobed into port A.

(ii)

Two computers exchange data using a

pair of 8255s. Port A works as a bidirectional

data port supported by appropriate handshaking signals.

The

appropriate modes of operation of the 8255 for (i) and (ii) would be

a.

Mode 0 for (i) and Mode 1 for

(ii)

b.

Mode 1 for (i) and Mode 2 for (ii)

c.

Mode 2 for (i) and Mode 0 for (ii)

d.

Mode 2 for (i) and Mode 1 for (ii)

Answer: B

Solution :

2. The number of memory cycles required to execute the

following 8085 instructions

(i)

LDA 3000H

(ii)

LXI D, F0F1H

Would be

a.

2 for (i) and 2 for (ii)

b.

4 for (i) and 3 for (ii)

c.

3 for (i) and 3 for (ii)

d.

3 for (i) and 4 for (ii)

Answer: B

Solution :

3. Consider the sequence of 8085 instructions given below.

LXI H, 9258H

MOV A, M

CMA

MOV M, A

Which one of the following is performed by this sequence of

instructions?

a.

Contents of location 9258 are moved

to the accumulator

b.

Contents of location 9258 are

compared with the contents of the accumulator

c.

Contents of location 9258 are

complemented and stored in location 9258

d.

Contents of location 5892 are

complemented and stored in location 5892.

Answer: C

Solution : https://www.youtube.com/watch?v=Us-RGGYexA8

4. It is desired to multiply the numbers 0AH by 0BH and store

the result in the accumulator. The numbers are available in registers B and C

respectively. A part of the 8085 program for this purpose is given below:

MVI A, 00H

LOOP: ..............

..............

..............

HLT

END

The sequence of instructions to complete the program would

be

a.

JNZ LOOP, ADD B, DCR

C

b.

ADDB, JNZ LOOP, DCR

C

c.

DCR C, JNZ LOOP, ADD

B

d.

ADD B, DCR C, JNZ

LOOP

Answer: D

2005

Statement

for linked Answer Questions 1 & 2 :

Consider an 8085 microprocessor system.

1. The following program starts at location 0100H.

LXI SP, 00FF

LXI H, 0701

MVI A, 20H

SUB M

THE Contents of accumulator when the program counter reaches

0109H is

a.

20H

b.

02H

c.

00H

d.

FFH

Answer: C

2. If in addition, following code exists from 0109H onwards.

ORI 40H

ADD M

What will be the result in the accumulator after executing

the last instruction?

a.

40H

b.

20H

c.

60H

d.

42H

Answer: C

Solution (1 & 2):

2006

1. An I/O peripheral device shown n figure (b) below is to be

interfaced to an 8085 microprocessor. To select the I/O device in the address

range D4H – D7H, its chip-select (CS’) should be connected to the output of the

decoder shown in the figure (a) below :

a.

Output 7

b.

Output 5

c.

Output 2

d.

Output 0

Answer: B

2. Following is the segment of a 8085 assembly language program

LXI

SP, EFFFH

CALL

3000H

:

:

3000H

: LXI H, 3CF4H

PUSH PSW

SPHL

POP PSW

RET

On the completion of RET instruction, the contents of SP is

a.

3CF0H

b.

3CF8H

c.

EFFDH

d.

EFFFH

Answer: B

Solution :

2007

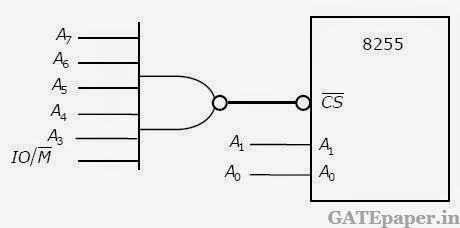

1. An 8255 chip is interfaced to an 8085 microprocessor system

as an I/O mapped I/O as shown in the figure. The address lines A0 and A1 of the

8085 are used by the 8255 chip to decode internally its three ports and the

control register. The address lines A0 to A7 as well as

the IO/M’ signal are used for address decoding. The range of addressees for

which the 8255 chip would get selected is

a.

F8H – FBH

b.

F8H – FCH

c.

F8H – FFH

d.

F0H – F7H

Answer: C

Statement for the linked answer questions 2 & 3 :

An 8085 assembly language program is given below.

Line 1 MVI A, B5H

2 MVI

B, 0EH

3 XRI

69H

4 ADD

B

5 ANI

9BH

6 CPI

9FH

7 STA

3010H

8 HLT

2. The contents of the accumulator just after execution of the

ADD instruction in line 4 will be

a.

C3H

b.

EAH

c.

DCH

d.

69H

Answer: B

3. After execution of line 7 of the program, the status of the

CY and Z flags will be ….. respectively.

a.

0, 0

b.

0, 1

c.

1, 0

d.

1, 1

Answer: C

2008

1. An 8085 executes the following instructions

2710 LXI H, 30A0H

2713 DAD H

2714 PCHL

All addresses and constants are in Hexa decimal. Let PC be

the contents of the program counter and HL be the contents of HL register pair

just after executing PCHL.

Which of the following statements is correct?

a.

PC = 2715H and HL = 30A0H

b.

PC = 30A0H and HL = 2715H

c.

PC = 6140H and HL = 6140H

d.

PC = 6140H and HL = 2715H

Answer: C

2009

1. In a microprocessor, the service routine for a certain

interrupt starts from a fixed location of memory which cannot be externally

set, but the interrupt can be delayed or rejected. Such an interrupt is

a.

non-maskable and non-vectored

b.

maskable and non-vectored

c.

non-maskable and vectored

d.

maskable and vectored

Answer: D

Solution : https://www.youtube.com/watch?v=pJ-6A_o5-LU

2010

1. For the 8085 assembly language program given below, the

content of the accumulator after the execution of the program is

3000 MVI A, 45H

3002 MOV B, A

3003 STC

3004 CMC

3005 RAR

3006 XRA B

a.

00H

b.

45H

c.

67H

d.

E7H

Answer: C

Solution : https://www.youtube.com/watch?v=NSdbNs_Oiwk

2011

1. An 8085 assembly language program is given below. Assume

that the carry flag is initially unset. The contents of the accumulator after

the execution of the program is

MVI A, 07H

RLC

MOV B, A

RLC

RLC

ADD B

RRC

a.

8CH

b.

64H

c.

23H

d.

15H

Answer: C

2013

1. For 8085 microprocessor, the following program is executed.

MVI A,05H

MVI B, 05H

PTR: ADD B

DCR B

JNZ PTR

ADI 03H

HLT

At the end of the program, accumulator contains

a.

17H

b.

20H

c.

23H

d.

05H

Answer: A

2014

1. For the 8085 microprocessor, the interfacing circuit to

input 8 – bit digital data (DI0 – DI7) from an external

device is shown in figure. The instruction for correct data transfer is

a.

MVI A, F8H

b.

IN F8H

c.

OUT F8H

d.

LDA F8F8H

Answer: D

Solution : https://www.youtube.com/watch?v=IH6ybT3DsAs

2. An 8085 microprocessor executes “STA 1234H” with starting

address location 1FFEH (STA copies the contents of the accumulator to the 16

bit address location). While the instruction is fetched and executed, the

sequence of values written at the address pins A15 - A8 is

Answer: A

Write a program execute the following additions, test CF, and then storage the results and

ReplyDeleteCF in memory location.

A. 30h + 15h

B. C3A0h + 10FDh

C. 7Fh + 1234h

C

DeleteAnalyse and Identify the addressing mode used in the following instructions:

ReplyDeletei)ADI 47H

ii)RRC

iii)LXI D, 2FFF H

Anyone know answer?

I) Immediate

DeleteII)Implicit

III)Immediate

1

ReplyDelete2

ReplyDeleteThe following instructions were executed on 8085 microprocessor. MVIB 05 H XRA A ADD B The accumulator value immediately after execution of last instruction is

ReplyDeleteOption 1:

01 H

Option 2: 10 H

Option 3: 05 H

Option 4: 50 H

Quick Navigation

Få

6

7

8

Backanaca

A 512 B RM connected to an 8085 microprocessor, with start address oooo H, assume the least two two significant address line connected to the chip select pin are missing, what is the end address of the last image?

ReplyDelete